A LEVEL COMPUTING

A LEVEL COMPUTING CPU architecture

CPU architecture

Theory

Theory

8. Superpipeline

The basic pipeline idea described on the last page is ok in theory, but not the best in practice.

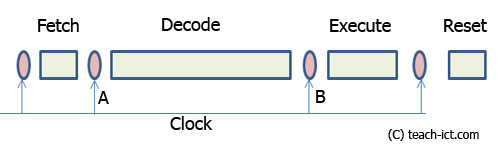

Consider a sketch of a basic pipeline below :

The pipeline is split up into fetch-decode-execute sections of unequal lengths. This is because each section is made up of a string of logic gates, and it takes more gates to do the decode than it does to fetch. Which means data takes longer to pass through that section.

The red bits represents points at which the clock is moving the data forward. So there is a subtle problem - the speed of the pipeline is determined by the longest (slowest) section.

Data at point A has to get to point B before the next clock tick. This means the maximum clock speed is limited by the time it takes to get from A to B (amongst other things).

Solution - the superpipeline

The answer engineers have come up with is to sub-divide the sections so each sub-division has roughly the same number of gates in series i.e. takes the same time to get across. This technique is called the 'superpipeline'.

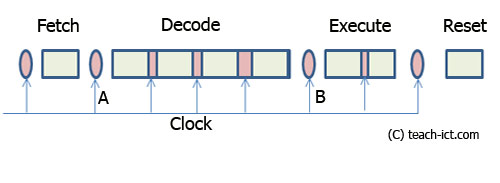

Now the pipeline looks like this

The picture shows the decode and execute sections divided into smaller chunks, with extra insert points for the clock to move the data. It is more complicated to design but now the clock speed can be increased because of the shorter time it take to cross each section, so CPU performance is much improved. The sub-division is called the 'pipeline depth'.

There is no perfect way to split up the pipeline and so chip makers come up with their own ideas

Here is a list of the pipeline depths of some modern CPUs

| Pipeline Depth | Processor |

|---|---|

| 10 | Athlon, Scorpion |

| 20 | Pentium 4 |

| 14 | UltraSPARC 3, Core 2 |

Challenge see if you can find out one extra fact on this topic that we haven't already told you

Click on this link: Superpipelined processor

Copyright © www.teach-ict.com