A LEVEL COMPUTING

A LEVEL COMPUTING CPU architecture

CPU architecture

Theory

Theory

7. Pipelining

The Von Neumann computer architecture is a sequential machine and it remains the most popular format for a CPU. Variations such as the Harvard architecture is used within a CPU to overcome some of the Von Neumann limitations.

But the chip makers are always looking to improve performance. Now that clock speed has more or less level out, another option is to try and run the instruction sequence as efficiently as possible. Hence the use of sophisticated cache design to try and make sure the CPU is kept busy. The other idea is to use parallelism - doing more than one thing at a time.

Every CPU carries out the Fetch-Decode-Execute-Reset cycle. But this takes a minimum of 4 cycles to complete.

But each operation involves separate parts of the CPU - the fetch involves the data and address bus - but the decode part does not care about that. And the Execute part of the CPU does not involve the hardware for the decode or fetch operation. So why not try to run them in parallel.

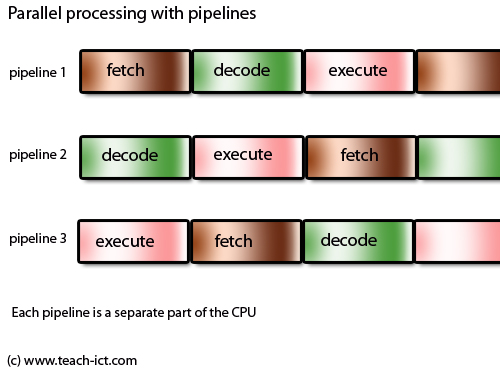

This is the idea of the 'pipeline' - stagger this cycle into three or more separate hardware processing paths within the CPU.

Whilst pipeline 1 is fetching the next instruction, pipeline 2 is decoding the previous one and pipeline 3 is executing the one before that.

As long as the pipelines can be kept full the CPU performance has increased three-fold without any change to the clock speed.

Challenge see if you can find out one extra fact on this topic that we haven't already told you

Click on this link: Pipelined CPU design

Copyright © www.teach-ict.com