A LEVEL COMPUTING

A LEVEL COMPUTING RISC and CISC

RISC and CISC

Theory

Theory

3. RISC

RISC stands for Reduced Instruction Set Computer.

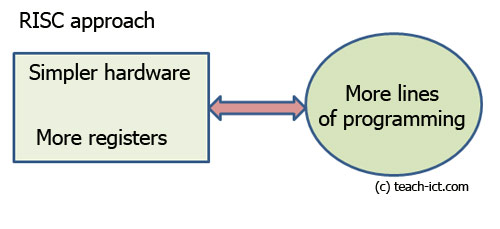

The general arrangement of a RISC machine is shown below.

Now the philosophy is reversed - design a relatively simple CPU decoder with many registers at the expense of having to write more lines of code to do the same thing.

The RISC approach has some significant advantages however. For example an instruction only takes a single cycle to complete compared to the multi-cycle cisc approach.

Consider a multiply command :

CISC: MULT a,b

Whilst doing the same thing with a RISC cpu needs a number of instructions

LOAD a from memory into register1 LOAD b from memory into a register2 PROD Register1, Register2 (multiply) STORE Answer back into memory |

This means more memory is needed to store the instructions, but they may actually run faster overall because each one only takes a single cycle. Furthermore, there is less movement in and out of main memory as there are more registers to hold temporary data.

Also the commands LOAD a and LOAD b are independent so there is an opportunity for parallel processing, thus improving performance

The downside is that the complier must convert a high level language instruction into many lines of machine code.

Challenge see if you can find out one extra fact on this topic that we haven't already told you

Click on this link: Design of a RISC computer

Copyright © www.teach-ict.com